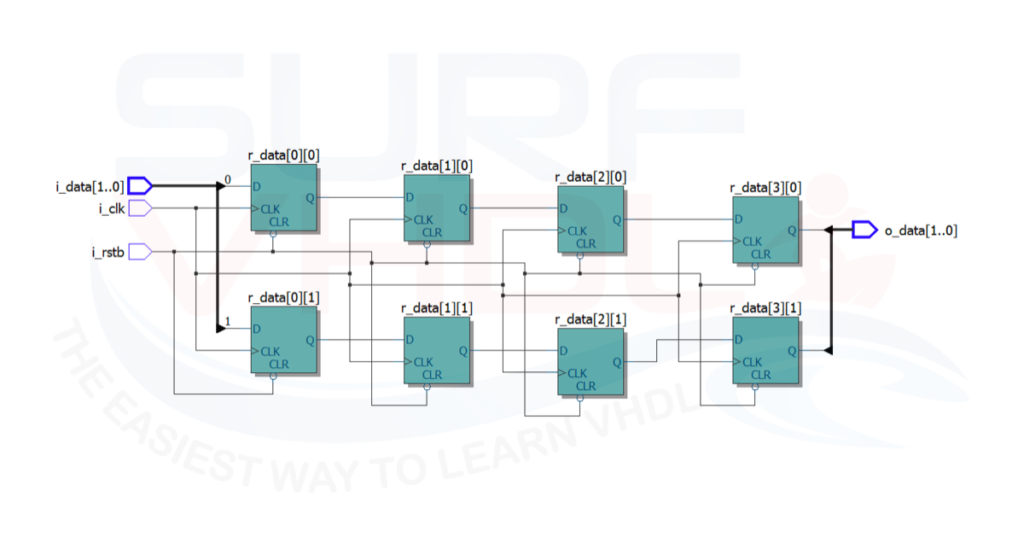

When that ’1’ is shifted out of the most significant position (position 0), the signal NEXT_HIGH_BIT is set to ’1’ and the conversion is complete. Before the conversion occurs, a ’1’ is placed in the least-significant bit position. In this implementation, the serial bits are shifted into place. The previous implementation used a counter to indicate the bit of the output that was set when a new serial bit was read. This design performs the same function as the previous one but uses a different algorithm to do the conversion. This example describes another implementation of the serial-to- parallel converter in the last example. Schematic Serial-to-Parallel Converter-Shifting Bits Serial-to-Parallel Converter-Shifting Bitsįigure A-18 Serial-to Parallet Converter-Counting Bits.Serial-to-Parallel Converter-Counting Bits.Soft Drink Machine-Count Nickels Version.Soft Drink Machine-State Machine Version.Understanding the Limitations of numeric_std package.Example 10-2: Unary Arithmetic Functions.Example 10-1: Binary Arithmetic Functions.synthesis_off and synthesis_on Directives.Translation Stop and Start Pragma Directives.Notation for Foundation Express Directives.Understanding Superset Issues and Error Checking.Differences Between Simulation and Synthesis.Arranging Expression Trees for Minimum Delay.Three-State Driver Without Registered Enable.Three-State Driver with Registered Enable.Understanding Limitations of Register Inference.Common Usage of a for.generate Statement.Steps in the Execution of a for.generate Statement.Concurrent Versions of Sequential Statements.Combinatorial Versus Sequential Processes.Example without Component Implication Directives.

Steps in the Execution of a for.loop Statement.Using the if Statement to Infer Registers and Latches.Examples of Architectures for NAND2 Entity.

0 kommentar(er)

0 kommentar(er)